Datasheet

QuickView Signoff Data Analysis Environment

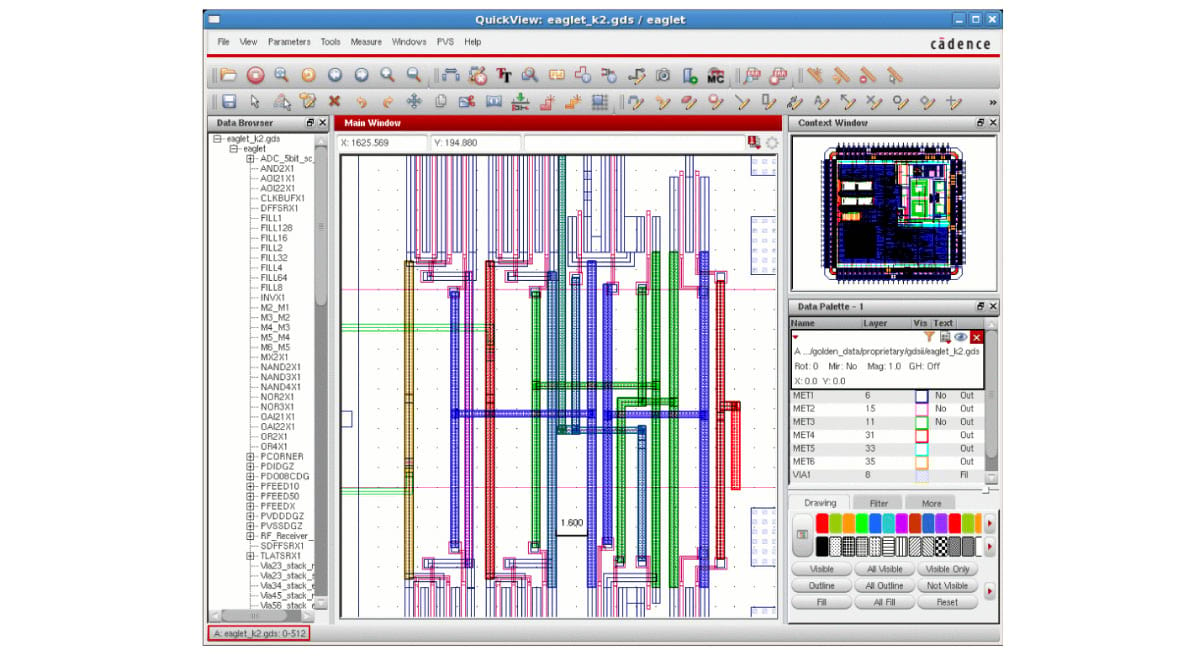

Easy-to-use, high-performance, and standalone chip-finishing system

Cadence QuickView Signoff Data Analysis Environment is an easy-to-use, high-performance, and standalone chip-finishing system that supports multiple formats of design, layout, and manufacturing data. The QuickView Signoff Data Analysis Environment loads large layouts (GDSII, OASIS, LEF/DEF, and manufacturing formats) in seconds and provides a rich set of debugging features, including net connectivity tracing, visualization, overlay, and GDSII/OASIS editing.

Overview

Overview

With the QuickView Signoff Data Analysis Environment’s high capacity, users can load extremely large layouts in seconds. The QuickView Signoff Data Analysis Environment’s signoff analysis environment allows users to place multiple layouts in one canvas and perform a range of chip-finishing functions.

The QuickView Signoff Data Analysis Environment is tightly integrated with the Cadence Physical Verification System (PVS) platform, and offers similar use models and flows to PVS in Cadence Encounter and Cadence Virtuoso platforms in a standalone capacity. It also works with third-party implementation and verification tools. The QuickView Signoff Data Analysis Environment’s high performance offers design and manufacturing teams a fast and extensible environment for efficient tapeout and chip finishing.