Interface-Aware Approach

Hierarchical approach to accelerate PCB design authoring and implementation

Key Benefits

- 15% faster design authoring and implementation

- Design PCBs at a much higher level of abstraction

- Faster routing of standards-based interfaces including DDR3, DDR4, SATA, and PCIe

If you’re a system designer, you are likely turning to protocols such as DDRx and PCI Express® (PCIe®) to support the performance, power, and bandwidth requirements of your products. Are your design authoring and layout tools delivering the speed and ease of use you need to keep pace with your design cycle demands? What if you could apply a hierarchical interface-aware approach to accelerate your PCB design authoring and implementation process—and increase design quality, performance, and reliability along the way?

Well, now you can with the Cadence® Allegro® PCB design flow—the latest version (16.65) has been enhanced with interface-aware design capabilities. The result? Up to 15% faster design authoring and implementation. The capability lets you design PCBs at a much higher level of abstraction, so you can achieve faster routing of standards-based interfaces including DDR3, DDR4, Serial ATA (SATA), and PCIe.

Supporting Today’s High-Speed Interfaces

Let’s take a look at how the interface-aware design capability works. Traditional design authoring tools work with buses or bundles and a single-level hierarchical definition of a group of signals. However, today’s interfaces can’t be modeled in a single-level hierarchy. Other challenges to address include the increasing number of constraints, increasing design density, shrinking pin pitches along with an increasing number of large pin-count devices, and increasing time to route designs (in the face of shrinking design cycle time and resources).

To connect interfaces quickly and easily, the hierarchical interface-aware design capability in the Allegro PCB design flow:

- Enables authoring at a higher level of abstraction to improve productivity

- Passes interface definition to layout designers

- Guides critical component placement and enables route planning

- Allows you to use auto-interactive technology to further accelerate breakout, routing, and tuning of interfaces

With the capability integrated, PCB schematic authoring technology in Allegro Design Entry HDL makes use of a new graphical object in the schematic, which allows you to instantiate interfaces and hierarchical netgroups, configure and connect interfaces to components and blocks, and apply interfaces to components.

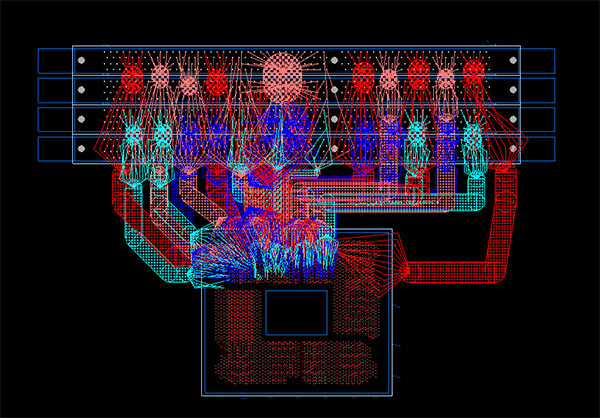

Since the capability supports multiple hierarchies, it becomes much easier to apply constraints to signals that are grouped in a logical manner. Allegro tools with the interface-aware capability—Allegro Design Authoring, Allegro Constraint Manager, and Allegro PCB Editor—automatically create and visually identify netgroups on the design canvas. The tools can also “nest” the netgroups to include sub-groups including byte lanes. You’ll be able to visualize the overall physical domain of an interface to see parts that are out of place. And with color-coding of netgroups, you can easily identify problematic areas and apply the proper layer distributions.

Summary

With the hierarchical interface-aware design capability available in the Allegro PCB design flow, routing high-speed interfaces such as DDRx and PCIe becomes a faster, more straightforward proposition. The capability supports PCB design at a higher level of abstraction, accelerates design authoring and implementation while providing visual indicators of placement, and enables you to identify routing problems earlier in your design cycle.

Training and Support

Need Help?

Training

The Training Learning Maps help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe

Online Support

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportTechnical Forums

Find community on the technical forums to discuss and elaborate on your design ideas.