FPGA Development

Comprehensive Flow for Complex FPGAs

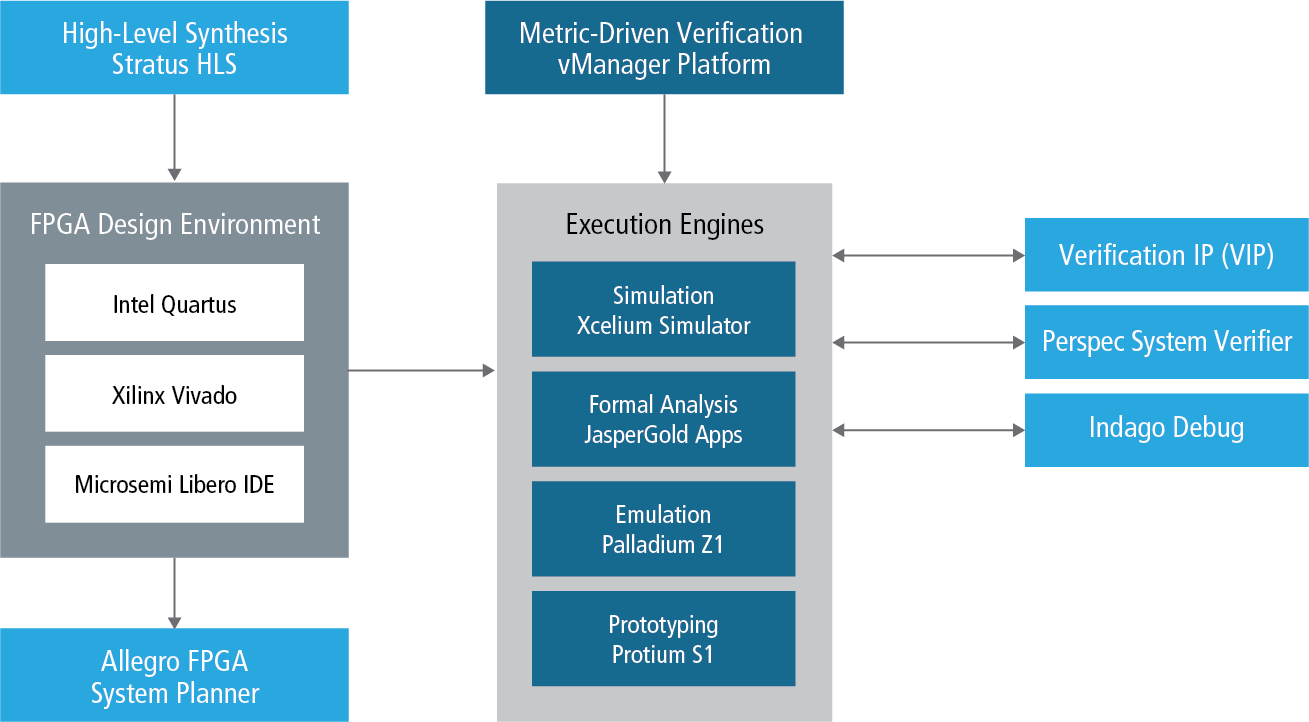

Key Benefits

- From system design, to verification, to board implementation flow

- Scalable verification methodology

- Native integration into FPGA vendor flows

- Complete set of tools and methodologies for DO-254 compliance

- Methodology and tool support for DO-254 verification requirements traceability

Due to the ever-increasing costs of development and manufacturing of custom IC devices as well as the flexibility that FPGAs provide, many system houses use FPGA devices not just for prototype or early availability runs, but for the entire life of the product. The result is the number of designs that are implemented in FPGAs is growing, and the complexity of those designs is increasing, requiring more powerful EDA tools for design, up-front verification, debug, and implementation.

Cadence offers a variety of tools and methodologies that enable users to develop their FPGA designs quickly and effectively to improve quality and time to FPGA signoff. Our tools and our FPGA vendor relationships help users avoid long programming and field testing cycles.

Let us help you:

- Track and sign off top-level requirements through all transformations for safety

- Use techniques and methodologies to improve design productivity

- Improve design creation and reuse of code

- Implement system synthesis that feeds FPGA synthesis tools

- Integrate coverage between formal and simulation increase coverage

Our portfolio includes:

- Ability to track requirements through signoff for high-reliability, safety-critical, or any complex FPGA design projects with the vManager™ Metric-Driven Signoff Platform

- Automatic creation of high-quality register-level (RTL) design implementations for FPGA designs with Stratus™ High-Level Synthesis

- Broad memory and protocol support with Cadence® design IP, memory IP, and verification IP (VIP)

- Formal verification through JasperGold® Apps to find more bugs in less time and earlier in the design process

- High-performance simulation with comprehensive VHDL, SystemVerilog, and other language support with the Xcelium™ Parallel Logic Simulator

- Rapid prototyping with debug and emulation congruence with Protium™ S1 FPGA-Based Prototyping Platform

- Fast system debug, acceleration, and emulation with Palladium® Z1 Enterprise Emulation Platform

- Rapid generation of system stimulus with the Perspec™ System Verifier

- Automatic pin assignment synthesis for rapid PCB development with the Allegro® FPGA System Planner