Datasheet

Spectre FX Simulator

Next-generation FastSPICE simulator delivering up to 3X productivity gains and high accuracy for memory and SoC designs

The Cadence Spectre FX Simulator is a next-generation transistor-level FastSPICE circuit simulator designed for pre- and post-layout verification of large-scale DRAM, flash, SRAM, and transistor-level SoC designs. The Spectre FX Simulator delivers up to 3X transient simulation performance with equivalent or superior accuracy over latest FastSPICE simulators as well as the ability to leverage up to 32 parallel CPU cores. With the addition of the Spectre FX Simulator, the industry-leading Spectre platform uniquely delivers a complete analog simulation solution offering seamless accuracy-performance continuum between the various verification tasks, from cell characterization through chip-level verification.

Overview

Spectre Simulation Platform

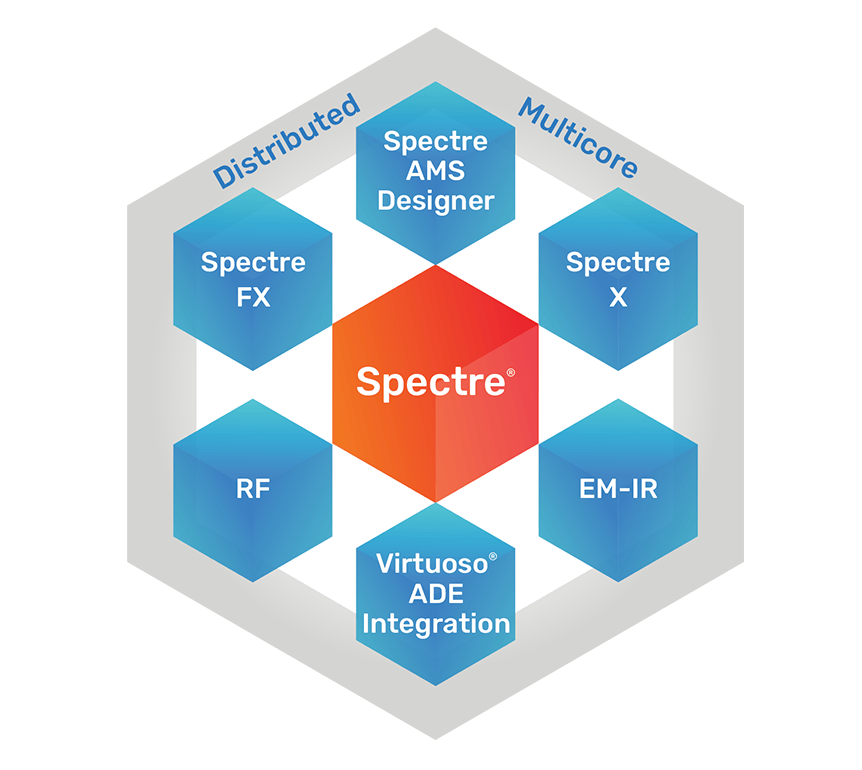

As the industry’s leading solution for balancing high-performance and -capacity needs with analog accuracy, the Spectre Simulation Platform encompasses multiple solvers to allow a designer to move easily and seamlessly between circuit-, block-, and system-level simulation and verification tasks. The foundation of the platform is a unified set of technologies shared by all of the simulators— the parser, device models, Verilog-A behavioral modeling, input data formats, output data formats, etc.—thereby guaranteeing consistent and accurate evaluation methods regardless of the simulator selected. In addition to individual solvers, the Spectre simulation technology is well integrated into other Cadence technology platforms, including Xcelium Logic Simulation, Liberate Trio Characterization Suite, Legato Reliability Solution, Virtuoso ADE Product Suite, Voltus-Fi Custom Power Integrity Solution, and the Virtuoso RF Solution to provide the industry’s most comprehensive cross-domain simulation solution.

Spectre FX Simulator

The Spectre FX Simulator uses a new groundbreaking architecture that employs innovative FastSPICE techniques including advanced partitioning and RC reduction algorithms to deliver up to 3X performance with equal or better accuracy versus latest FastSPICE products. Using the Spectre FX Simulator, design teams can accurately and efficiently verify functionality, timing, and power as well as other attributes of their memory and SoC designs for signoff. Advanced partitioning, multi-rate, and other next-generation FastSPICE algorithms are used to find the optimal balance between accuracy and speed of the simulation. The Spectre FX Simulator also delivers high capacity to handle large-scale memories and SoCs. Stateof-the art RC reduction techniques enable matrix size reduction without sacrificing accuracy to address large post-layout designs. The Spectre FX Simulator’s highly scalable multi-core architecture allows parallelization of transient simulations up to 32 cores, enabling design and verification teams to improve the simulation turnaround time by utilizing the hardware resources available without trading off accuracy. The Spectre FX Simulator is an integral part of the Spectre Simulation Platform and is built on the same infrastructure technology as all members of the Spectre family of simulators.

Benefits

Features

Best-in-class use model with minimal tuning

The Spectre FX Simulator delivers a best-in-class use model with excellent accuracy and performance balance for FastSPICE verification with minimal tuning needed for any given application. Out of the box, the simulator offers excellent simulation speed with high accuracy for most FastSPICE applications. The simulator also offers presets for designers to control the tradeoff between simulation accuracy and performance in a predictable manner. Designers can pick the right preset to use depending on the verification task—leakage current measurement or timing checks, for example. The presets can also be set at the block level of a design to obtain even more fine-grained control on the simulator’s accuracy-performance tradeoff for specific debugging purposes. In addition, the simulator offers SPICE and FastSPICE modes to further aid in debugging of design issues or establish golden reference while doing functional verification.

Fully compatible with existing verification flows

The simulator leverages the Spectre platform’s solid accuracy foundation that designers have trusted for almost 30 years. The Spectre FX Simulator reuses the Spectre platform front-end and back-end infrastructure to provide full compatibility with the existing Spectre and SPICE flows. It is also tightly integrated into the Virtuoso ADE Product Suite to provide a seamless experience for analog designers and verification engineers.

Post-layout simulation

Modern designs manufactured on advanced process nodes need to be verified with post-layout parasitics to account for layout and interconnect effects that significantly impact timing, power, and other attributes. The Spectre FX Simulator delivers the high capacity needed to handle several tens of millions of RC parasitics and supports post-layout simulation with DSPF, SPEF, and extracted SPICE formats. The parasitics file can be a flat or hierarchical netlist included directly in the main netlist or can be back-annotated into a pre-layout netlist for improved debuggability. The simulation employs proprietary RC reduction techniques in combination with an advanced matrix solver optimized for RC simulation to accelerate post-layout simulation.

Transistor-level dynamic and static circuit checks

The Spectre FX Simulator offers extensive verification capabilities to expand the scope of verification coverage for memories and SoC designs beyond timing and functionality checks. Both static and dynamic circuit checking commands allow designers to detect conditions such as high impedance nodes, leakage paths between power supplies, and device-level timing errors. These circuit checks can be applied either globally to the entire design, or locally to specific blocks of the design.

Debugging capabilities

The Spectre FX Simulator offers many debugging capabilities to find and fix design problems quickly and effectively. The Tcl interactive mode allows run-time debugging like adding new probes, starting and stopping the simulation, and adding new design elements such as voltage sources. The simulator also supports the save-restore feature that allows restarting from a saved state to save computation time. The save-restore feature also allows debugging design issues faster by allowing small design changes and different accuracy settings between save and restore simulations.