Datasheet

Sigrity Aurora IC Package Analysis

In-design signal and power integrity analysis for IC packages

Cadence Sigrity Aurora IC Package Analysis provides traditional signal and power integrity (SI/PI) analysis for IC package pre-layout, in-design, and post-layout. Integrated with Cadence Allegro X Advanced Package Designer editing and routing technologies, Sigrity Aurora IC Package Analysis enables users to start analyzing earlier in the design cycle using “what if” exploration scenarios to set more accurate constraints and reduce iterations. This methodology empowers IC package design teams to meet project deadlines even when SI and PI specialists may not be readily available.

Overview

Overview

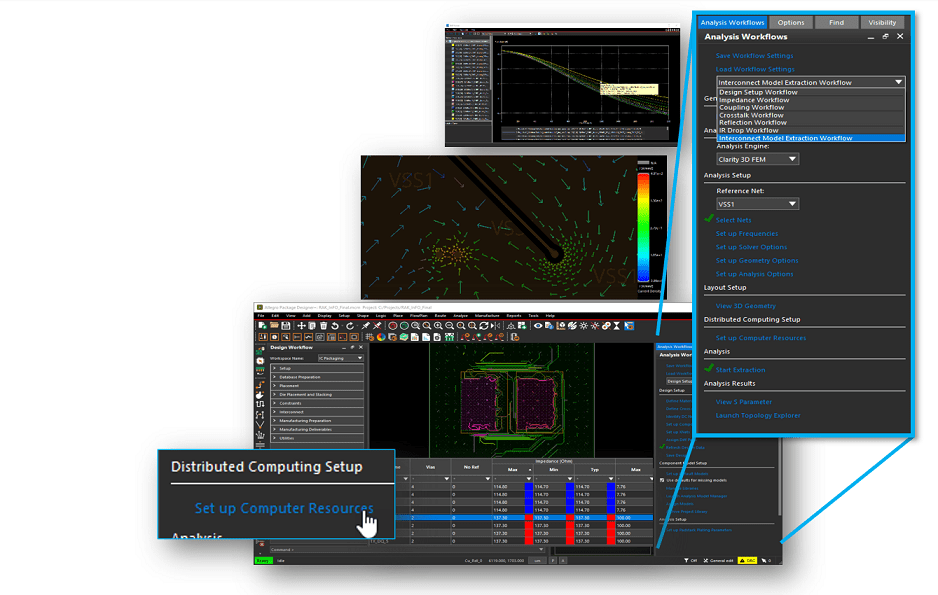

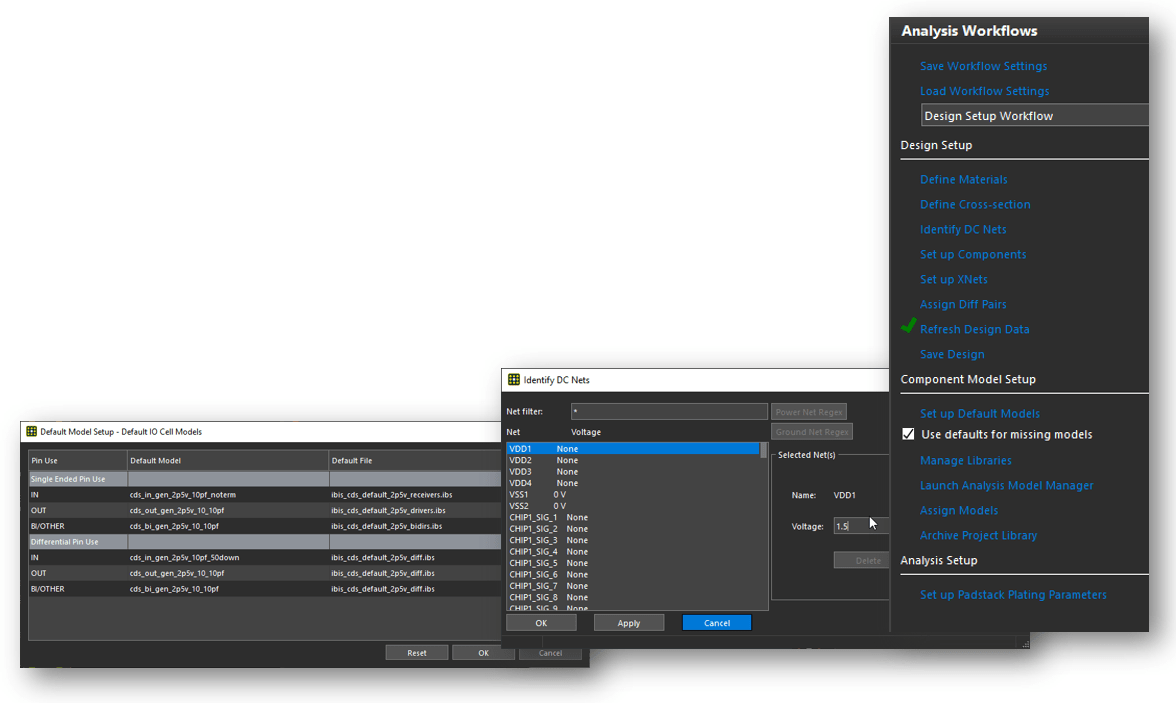

Sigrity Aurora IC Package Analysis provides a SPICE-based simulator and the patented Sigrity embedded hybrid field solvers for the extraction of 2D and 3D structures. Power-aware IBIS (behavioral) models are supported, as well as transistor-level models, if necessary. High-speed signals can be explored pre-layout to compare alternatives, or post-layout for a comprehensive analysis of all associated signals. It provides in-design analysis to Allegro X Advanced Package Designer layout environment with integrated Sigrity analysis engines. (Figure 1).

To succeed in today’s highly competitive electronics markets, simulation and analysis is now being shifted to the earliest stages of the design process using an in-design analysis (IDA) methodology, where analysis and simulation are moved from an afterthought in the workflow to an integral part of each phase of the design process. Sigrity Aurora IC Package Analysis provides IDA to Allegro X Advanced Package Designer layout environment with integrated Sigrity analysis engines.

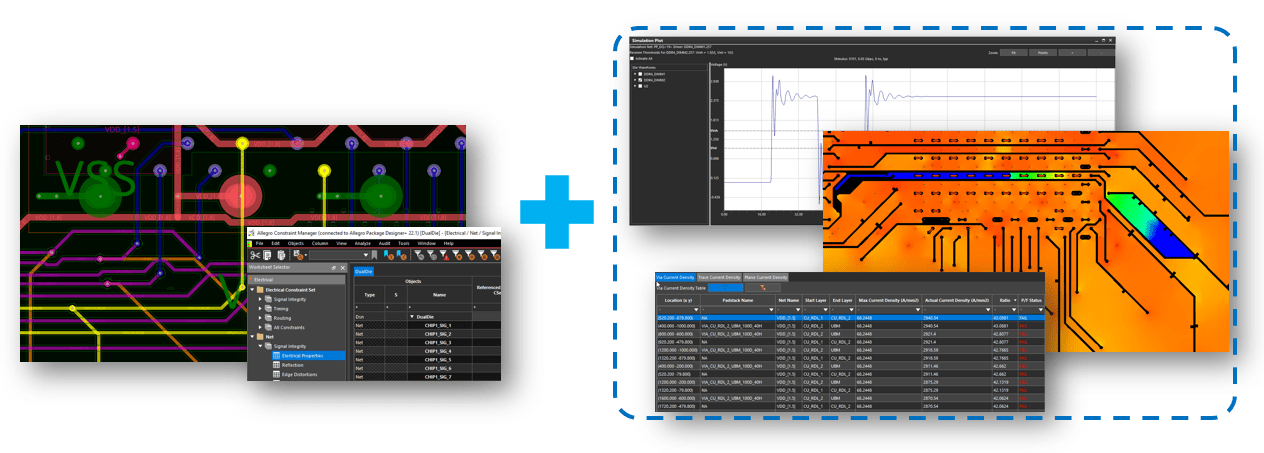

Integrated IDA Methodologies

Sigrity Aurora IC Package Analysis enables designers to boost their efficiency and avoid manual re-entry mistakes. Sigrity simulations engines within Allegro X Advanced Package Designer offer easy-to-use IDA methodologies integrated within the Allegro environment that empower IC package designers to quickly detect and address potential electrical problems as the design progresses from beginning to end, enabling them to correct basic SI/PI issues by themselves. It is directly integrated into the package design framework and simulation results are presented as “visions” overlays with integrated fundamental SI/PI analysis flows (Figure 2).

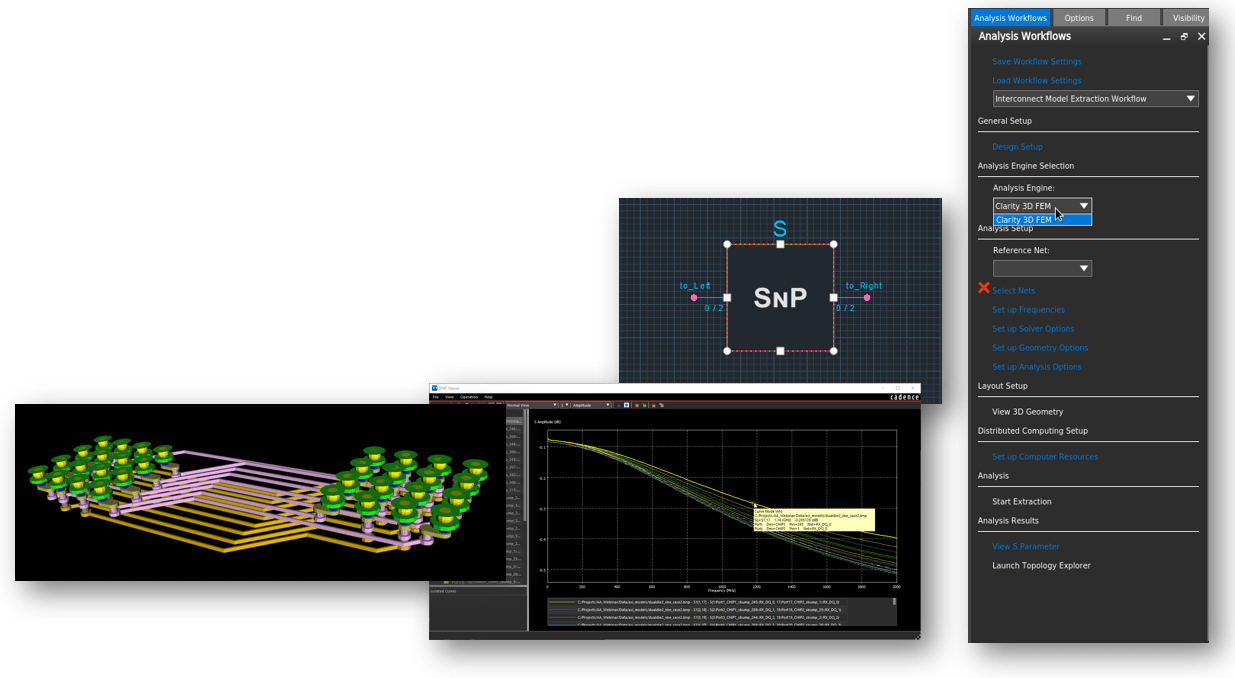

Interconnect Model Extraction

The interconnect model extraction capability makes full-wave 3D interconnect model extraction easy, while support for distributed computing accelerates this powerful feature (Figure 3). Fully automatic port definitions and de-embedding are supported, along with the ability to view 3D geometry and S-parameters. The Sigrity Topology Explorer (TopXp) can be launched from within the environment.

Features

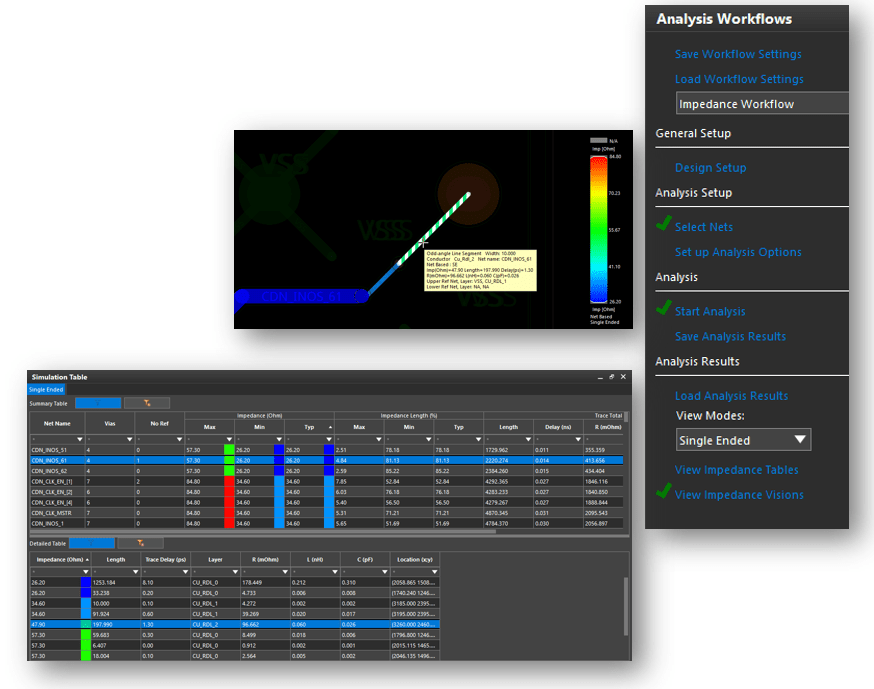

Impedance Analysis Screening

The analysis screening feature requires no SI models. It provides a global view of results and more accessible graphic overlays, tables, and plots. Results can be sorted to easily locate outliers (Figure 4).

Coupling Analysis Screening

The coupling analysis screening quickly scans the design for cases of excessive coupling between signals. A global view of results is provided with graphics, tables, and plots.

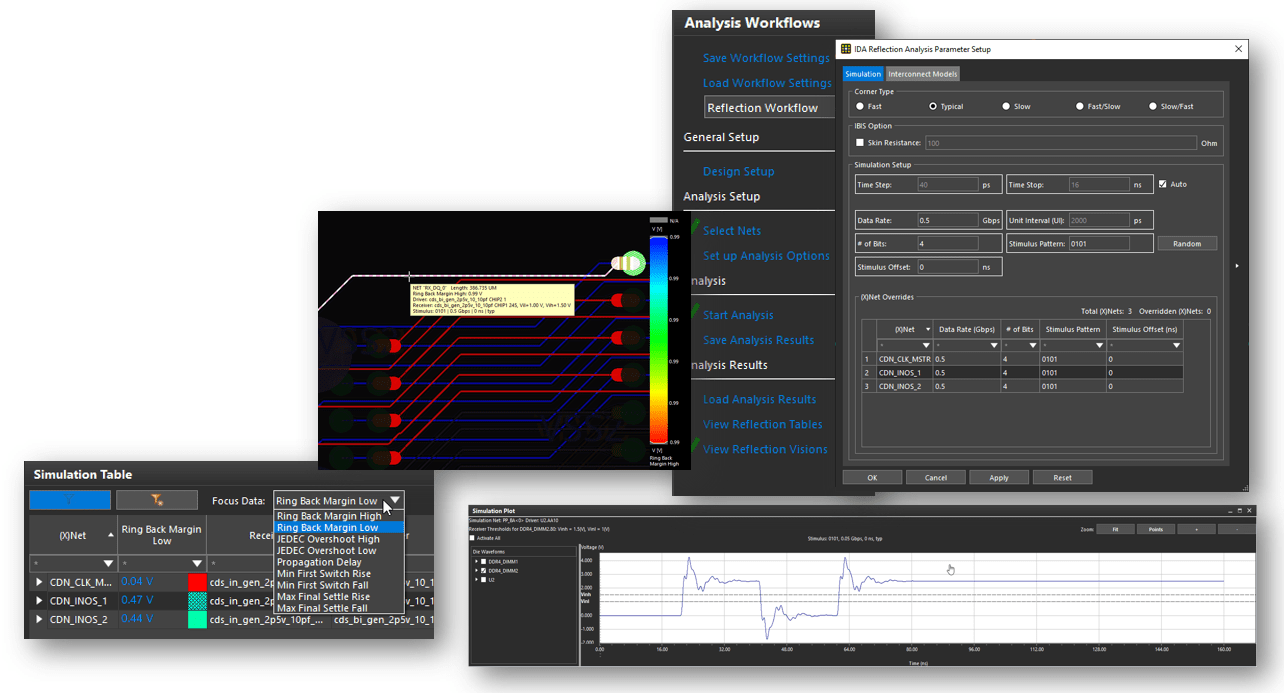

Reflection Analysis

Reflection analysis utilizes SI models to simulate selected signals and enables designers to sort and analyze results to find outliers for various signal quality metrics. Additional abilities include waveform viewing, batch simulation, tooltips that show results details, and the ability to use default or specific I/O models (Figure 5).

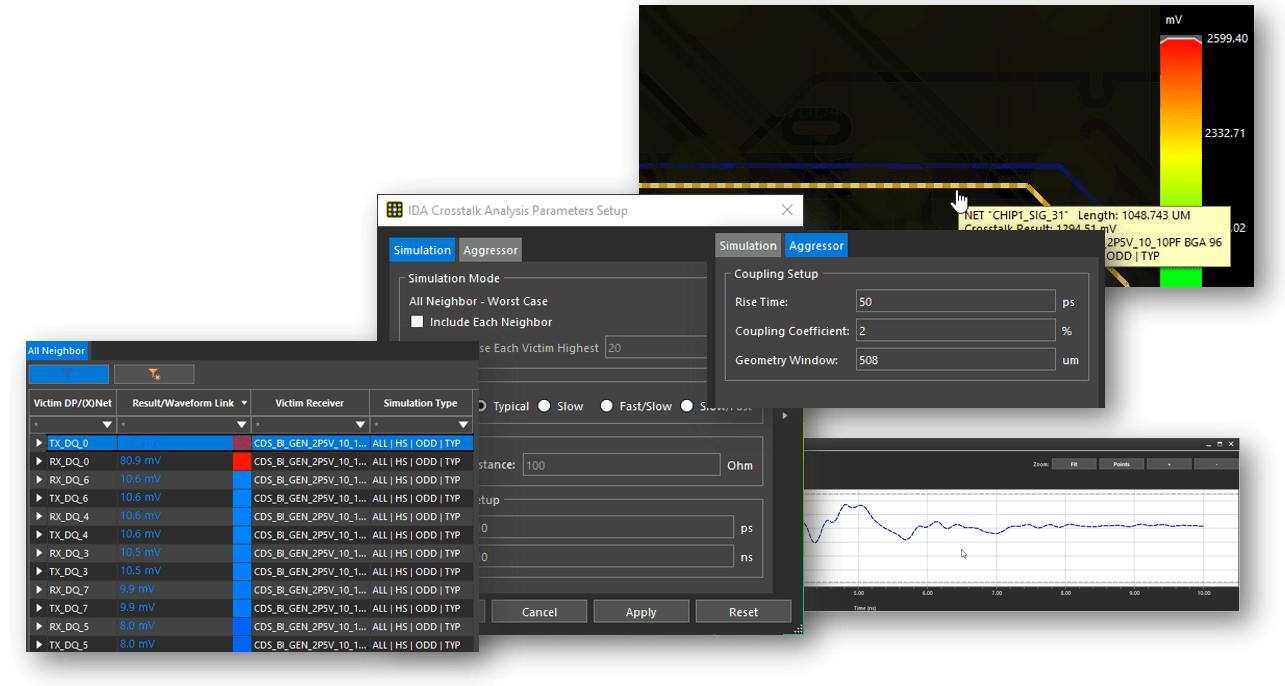

Crosstalk Analysis

The crosstalk analysis feature allows designers to use either default or specific I/O models to identify victim crosstalk nets and individual and worst-case aggressors. Crosstalk simulation waveforms can be viewed (Figure 6).

IR Drop Analysis

The IR drop analysis feature provides IR drop, absolute voltage, current density, and current view modes. Current vectors, non-deal ground support, and pass/fail constraints are also offered (Figure 7).