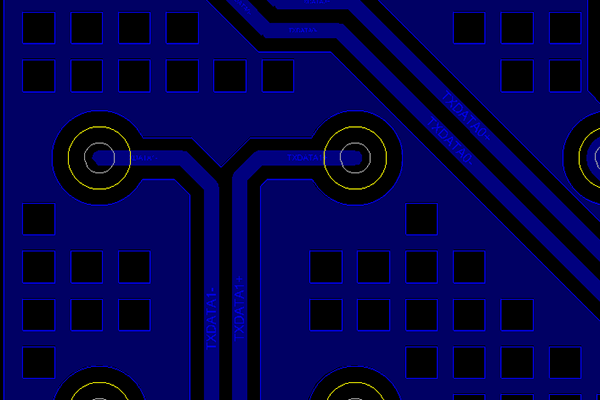

ケイデンスの設計技術によるInFOパッケージ技術

ケイデンスのICレベルおよびパッケージ設計ツールを使用した統合設計フローにより、InFoテクノロジーの機能強化によるシームレスなフローを提供し、設計全体の所要時間を短縮

ケイデンスは、以下を使用してTSMCの統合ファンアウト(InFO)パッケージングテクノロジーの幅広い展開を可能にしています。

- Cadence® Physical Verification System (PVS)

- Cadence System-in-Package (SiP)

- SiP Layout Wafer-Level Chip-Scale Package (WLCSP) Option

- Sigrity™ IC package analysis and 3D modeling

- Voltus™ IC Power Integrity Solution

InFOテクノロジーとはどのようなものですか?

TSMCのInFOテクノロジーは、熱抵抗が低く、RF材料の特性が非常に高く、極薄の厚さを提供するファンアウト、シングル、マルチダイ、またはPoP (package-on-package)ウェーハレベルのチップスケールパッケージ技術です。 薄型デバイスやデバイススタックが必要なお客様のニーズを満たし、パフォーマンスを最適化し、モバイルコンピューティング製品のコストを削減します。

InFOテクノロジーが設計者視点と異なるのは何ですか?

- きわめて薄いパッケージ基板を提供するために、密に制御された限局性のメタル密度

- TSMCは、ICアートワークの専門知識、ツールセット、およびフローを活用してこれらのデバイスを製造しています

テクノロジーの有効化

TSMCのユーザーがこれらの要件を満たすことを可能にするために、ケイデンスは次の新しい機能と更新機能を提供します。

- SiP ICパッケージレイアウトツールでは、InFOテクノロジーの厳しい密度要件を満たすために、デザインの各レイヤーのローカライズされたメタル密度をスキャン、評価、修正するためのツールを追加しました

- ICパッケージング設計ツールとサインオフPVS DRC / LVSの緊密な統合を実現し、設計サイクル時間を短縮

- 包括的なエレクトロマイグレーションおよびIRドロップ(EM / IR)デザインルールと要件をサポートしフルチップSoC(System-On-Chip)パワーサインオフ精度を提供するセルレベルのパワーインテグリティツール