- Overview

- Tempus DRA Suite Benefits

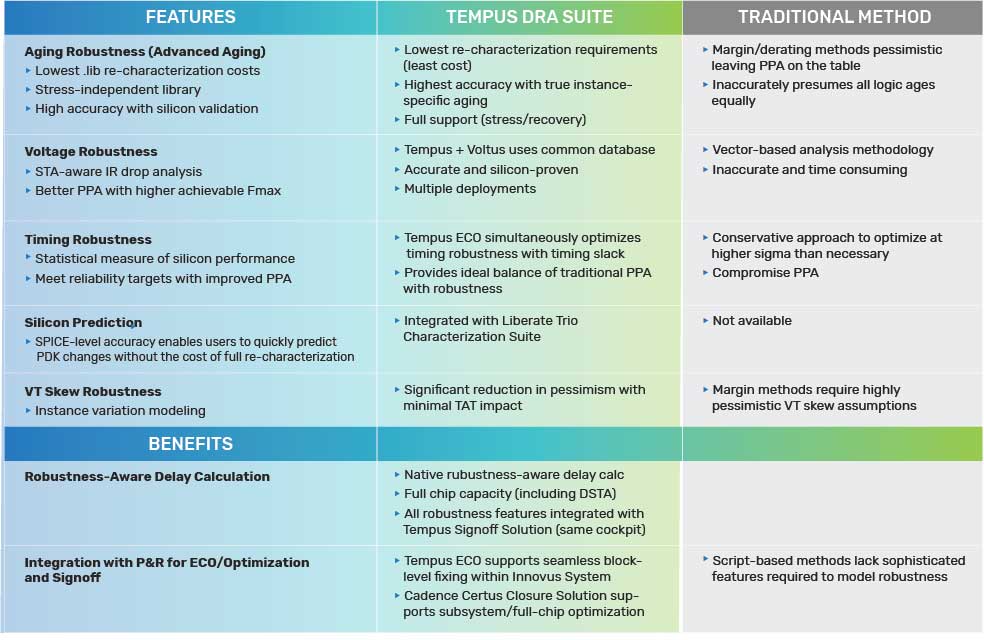

- Aging Robustness – Improve PPA by Up to 10% Through Accurate Aging Analysis

- Voltage Robustness – STA-Aware IR Drop Analysis

- Timing Robustness – Statistical Measurement of Silicon Performance

- Silicon Prediction – Process Drift Modeling and Prediction Plus Model-to-Hardware Correlation

- VT Skew Robustness - Advanced Techniques Addressing Pessimistic STA Methodology

Technical Brief

Cadence Tempus Design Robustness Analysis Suiteで最高レベルのPPAを実現

Cadence Tempus Design Robustness Analysis (DRA) Suiteは、シリコンの経年劣化やプロセスのばらつきなど、設計性能に影響を与える重要な現象に対するサインオフ解析と最適化を提供します。高精度なモデルを提供するため、設計エンジニアはクラス最高の消費電力、性能、面積(PPA)を達成しながら、サインオフすることができます。

Overview

概要

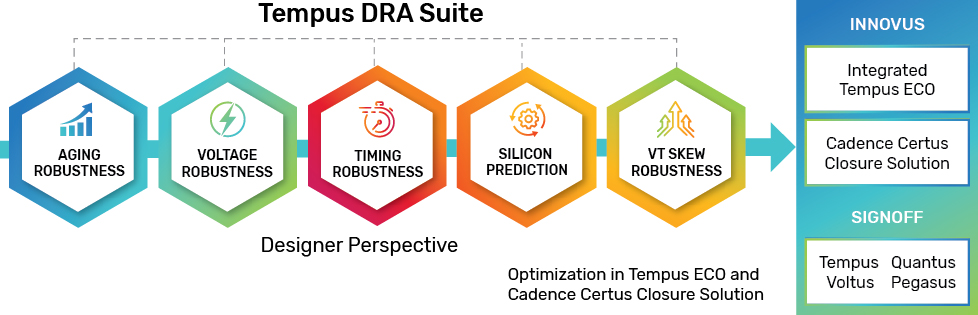

Tempus DRA Suiteは、経年劣化ロバストネス、電圧ロバストネス、タイミングロバストネス、シリコン予測、VTスキュー・ロバストネスの5つの高度なタイミング解析から構成されています。このスイートの高度なタイミングモデルにより、設計エンジニアは、ディレートやマージンといった従来のアプローチと比較して、悲観的な見方を大幅に減らしながら、これらの影響を正確に解析することができます。さらに、設計エンジニアはタイミング・データを使用して、Cadence Innovus Implementation System内のTempus ECOオプションまたはCadence Certus Closure Solutionを使用して、最適化とサインオフ・クロージャーを行うことができます。この統合されたアプローチにより、ブロックレベルからサブシステムレベル/フルチップデザインまで、最良のPPAと最速のクロージャを行えます。

経年劣化に対するロバスト性 - 正確な経年劣化分析によりPPAを最大10%改善

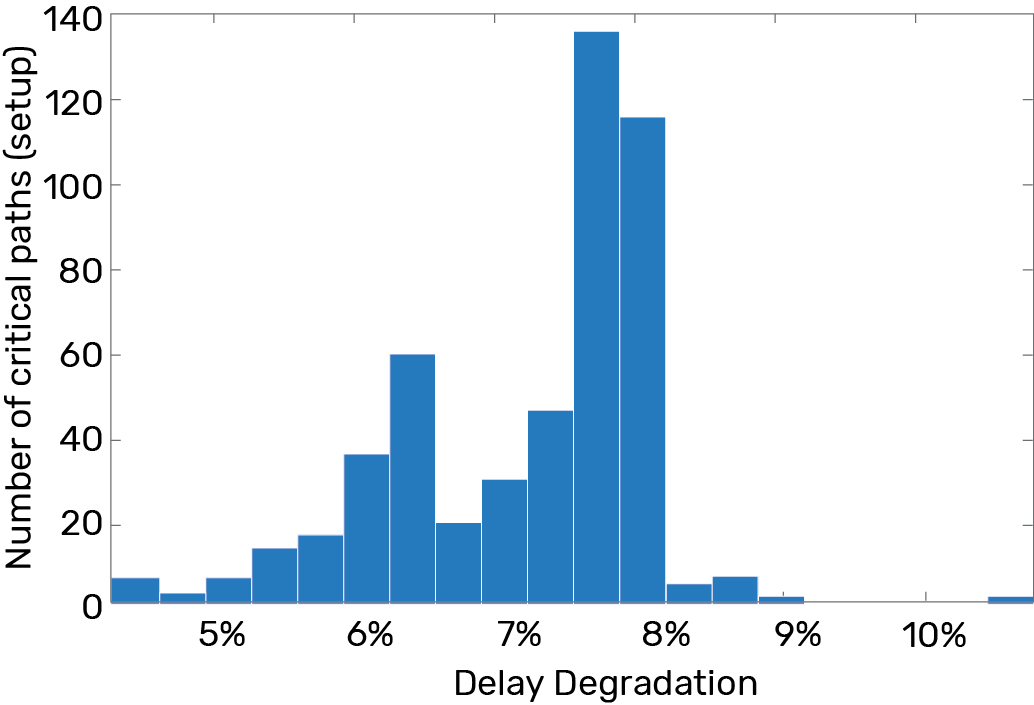

業界をリードする初の解析機能である経年劣化ロバストネスは、自動車、航空宇宙、民生、モバイル、ハイパースケール設計に存在する経年劣化の課題に正確に対処する画期的な技術を提供します。経年劣化ロバストネスは、著しく不正確なマージンの代わりに、回路性能に対する経年劣化の影響を正確に計算し、同時に設計のPPAを改善します。解析は、ファウンドリ固有のSPICE信頼性モデルに基づいて、Cadence Liberate Library Characterization Flowで経年劣化ストレスに依存しないライブラリ・モデルをキャプチャすることから始まります。次に、設計エンジニアはTempus Timing Solution内で非均一エージングおよびリカバリ・モデルを使用して設計性能を測定します。最後に、設計者はTempus ECOとInnovus Implementation Systemフロー内で、経年劣化したPPAと新しいPPAを同時に最適化します。経年劣化ロバスト性により、従来の経年劣化手法の過剰設計を回避し、より迅速な設計終結と優れたPPAを実現することができます。

電圧ロバスト性 - STAを考慮したIRドロップ解析

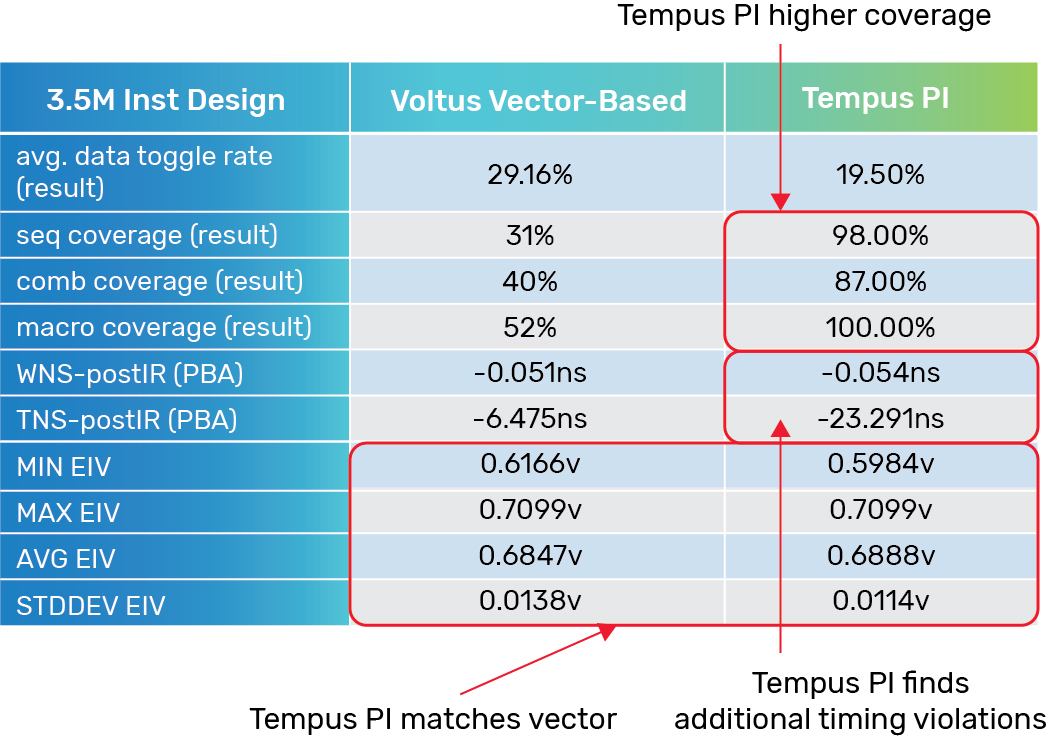

電圧ロバストネス解析機能は、世界で初めてIRドロップ解析と修正技術を統合し、真のサインオフ機能を提供します。Tempus Power Integrity (PI)とVoltus IC Power Integrityソリューションのシームレスな統合により、電圧ロバスト性はIRドロップが回路性能に与える影響を解析し、デッドシリコンの原因となる従来のIRドロップサインオフ手法では見逃されていたタイミング違反を検出します。さらに、電圧ロバスト性はTempus ECOと統合され、最高のPPAを達成しながら、タイミング違反とIRドロップ違反の両方を削減します。

タイミングロバスト性 -シリコン性能の統計的測定

Tempus DRA Suiteの3つ目の解析機能であるタイミング・ロバストネスは、従来のSPICEモンテカルロ解析のキャパシティ制限を克服し、デザイン全体の相関遅延ばらつきをキャプチャします。設計者は、タイミング・ロバストネスをTempus ECOと組み合わせて使用することで、PPAを改善しながらばらつきを最適化し、タイミング・クロージャECOサイクルを高速化することができます。

シリコン予測 - プロセス・ドリフトのモデリングと予測、さらにモデルとハードウェアの相関関係

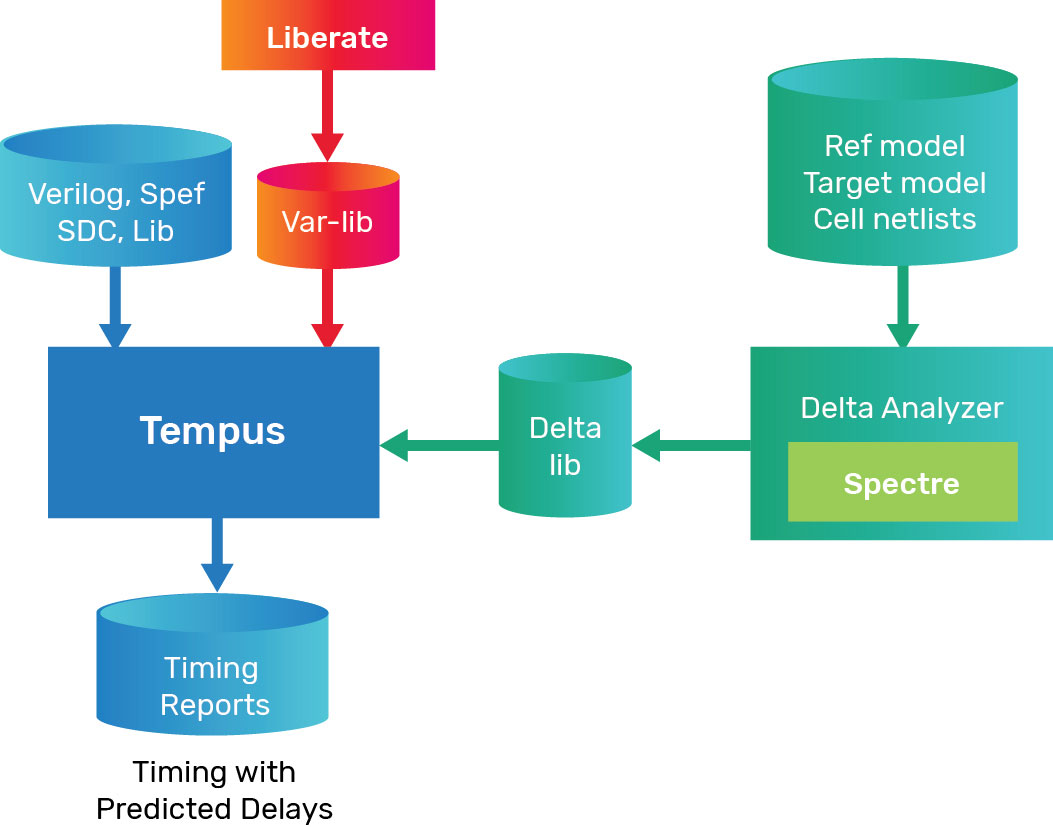

シリコン予測は、Tempus DRA Suiteの4番目の解析機能で、設計エンジニアに一連のPDKリビジョンにおける回路性能を予測解析する手法を提供します。シリコン予測は、Liberate Library Characterization FlowとTempus Timing Solutionの統合を活用し、特定された離散パラメータの正確な統計モデルを提供します。これにより、設計エンジニアは、パラメータの変更が設計全体の性能に与える影響を迅速に評価することができます。さらに、シリコン予測により、設計エンジニアはTempus STA環境とテストシリコンの間でモデルからハードウェアへの相関を実行できます。シリコン予測を使用することで、チームは正確なシリコンモデルを使用して予測された遅延で真のサインオフとPPA最適化を実行できるようになります。

VTスキュー・ロバストネス -緻密なSTA手法に対応する高度なテクニック

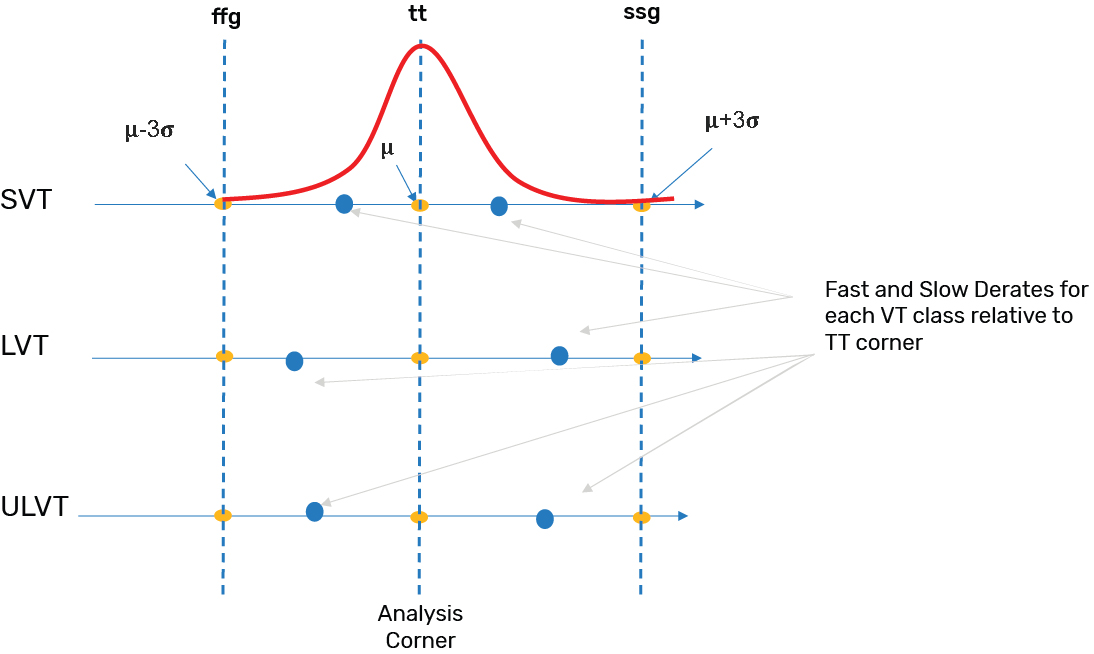

VTスキュー・ロバストネスは、Tempus DRA Suiteの5番目の解析機能で、クロックツリー内に複数のVTクラスライブラリを使用する設計のばらつきをより正確にモデル化します。VTスキュー・ロバストネスを使用して、設計者はVTクラスとそれに関連するファスト・ディレートとスロー・ディレートを定義します。その後、VTスキュー・ロバストネスは、インテリジェントに列挙された一連の解析を実行し、起動パスとキャプチャ・パスの構成に基づいてワーストケースのスラックを決定します。この高度なアプローチは、従来のSTAサインオフ手法に比べて信頼性を高め、悲観的な見方を減らすことができます。